# A HIGH-RESOLUTION TIME TO DIGITAL CONVERTER DESIGN FOR ALL DIGITAL PHASE-

# LOCKED LOOPS

# A THESIS SUBMITTED TO

# THE GRADUATE SCHOOL OF

# ENGINEERING AND NATURAL SCIENCES

# OF ISTANBUL MEDIPOL UNIVERSITY

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR

# THE DEGREE OF

# MASTER OF SCIENCE

IN

# ELECTRICAL, ELECTRONICS ENGINEERING AND CYBER SYSTEMS

By

Tamer Eren

June, 2021

# A HIGH-RESOLUTION TIME TO DIGITAL CONVERTER DESIGN FOR ALL DIGITAL PHASE-LOCKED LOOPS

By Tamer Eren

30 June 2021

We certify that we have read this dissertation and that in our opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Master of Science.

Assoc. Prof. Dr. Hakan Doğan (Advisor)

Assoc. Prof. Dr. Tufan Coşkun Karalar

Assist. Prof. Dr. Hüseyin Şerif Savcı

Approved by the Graduate School of Engineering and Natural Sciences:

Assoc. Prof. Dr. Yasemin Yüksel Durmaz

Director of the Graduate School of Engineering and Natural Sciences

I hereby declare that all information in this document has been obtained and presented in accordance with the academic rules and ethical conduct. I also declare that, as required by these rules and conduct, I have fully cited and referenced all material and results that are not original to this work.

Signature

Name, Surname: TAMER EREN

:

# ACKNOWLEDGEMENT

The completion of this master thesis could not have been possible without the significant assistance of so many people around me. Unfortunately, enumerating them impossible because of limitations but their contributions are gratefully appreciated.

Before anyone, I submit my heartiest gratitude to Assoc. Prof. Hakan DOĞAN, who shared and taught me everything about this field expertly. I also owe him a lot, for his patience and tolerance for my endless and timeless questions.

Another person I cannot continue without expressing my high gratitude to is Dr. Mustafa AKTAN. Whenever I tried to solve any problem during the thesis, he instantly helped me without hesitation. His guidance through this project is incomparable to anyone else.

Also, my teammate, Zehra Nur OKTAY deserves special thanks for her motivations for maintaining a positive atmosphere during the research and for being a very good support for me in every difficult situation.

Finally, I would like to serve my deep gratitude to my mom, wife, and family for their countless and immeasurable contributions from the beginning of my education.

This thesis was funded by ASELSAN

Tamer Eren June, 2021

# CONTENTS

# Page

| ACKNO   | WLEDGEMENT                                    | iv      |

|---------|-----------------------------------------------|---------|

|         | ITS                                           |         |

| LIST OF | FIGURES                                       | vii     |

|         | TABLES                                        |         |

|         | SYMBOLS                                       |         |

| ABBREV  | IATIONS                                       | xi      |

| ÖZET    |                                               | xii     |

|         | СТ                                            |         |

|         | RODUCTION                                     |         |

|         | ORETICAL PART                                 |         |

|         | Phase-Locked Loop Systems                     |         |

| 2.1.1   | · · · · · · · · · · · · · · · · · · ·         |         |

|         | Usage of PLLs                                 |         |

| 2.1.3   | . Types of Phase-Locked Loops                 |         |

|         | .3.1. Analog PLL blocks                       |         |

| 2.1     | .3.2. Digital and All-Digital PLL blocks      | 14      |

| 2.2.    | Time-to-Digital Converters                    | 17      |

| 2.2.1   | · · · · · · · · · · · · · · · · · · ·         | rsion18 |

| 2.2     | 2.1.1. Resolution                             |         |

| 2.2     | 2.1.2. Output bits                            |         |

| 2.2     | 2.1.3. Linearity and non-linearity            |         |

| 2.2     | 2.1.4. DC accuracy                            |         |

| 2.2     | 2.1.5. Power and area                         |         |

| 2.2     | 2.1.6. Dead time and counting rate            |         |

| 2.2.2   |                                               |         |

| 2.2.3   | . Working principle of classical TDCs         | 25      |

| 2.2.4   | . Time-to-Digital Converters architectures    |         |

| 2.2     | 2.4.1. Counter-based TDC                      |         |

| 2.2     | 2.4.2. Analog-to-digital conversion-based TDC |         |

| 2.2     | 2.4.3. Delay-line based TDCs                  |         |

| 2.2     | 2.4.4. Ring Oscillator based TDCs             |         |

|         | 2.4.5. 2-D Vernier based TDCs                 |         |

|         | 2.4.6. Time amplifier based TDCs              |         |

|         | 2.4.7. Two-step TDC circuit                   |         |

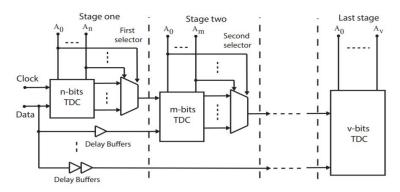

|         | 2.4.8. Multi-step TDC circuit                 |         |

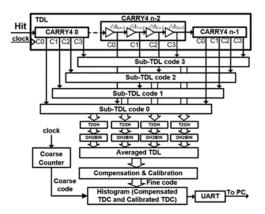

| 2.2     | 2.4.9. FPGA based TDCs                        |         |

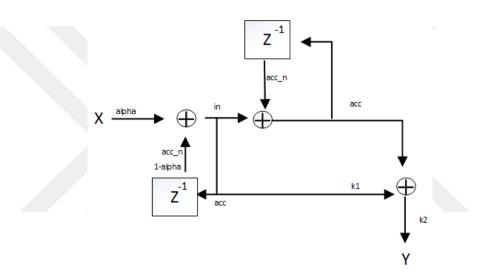

|         | 2.4.10. Algorithmic TDCs                      |         |

|         | ERIMENTAL PART                                |         |

|         | The proposed TDC architecture                 |         |

|         | Ring Oscillator                               |         |

|         | D-Flipflop array for fine difference          |         |

|         | Hamming Distance                              |         |

|         | D-Flipflop array for coarse difference        |         |

|         | Manual Transformation block                   |         |

|         | Phase-Frequency Detector                      |         |

|         | Frequency Detector                            |         |

| 3.9.    | Error Controller                              | 53      |

| 4. <b>RESUL</b> | <b>FS AND DISCUSSION</b>                                       | 55  |

|-----------------|----------------------------------------------------------------|-----|

| 4.1. Fun        | ctional Test Results                                           | 55  |

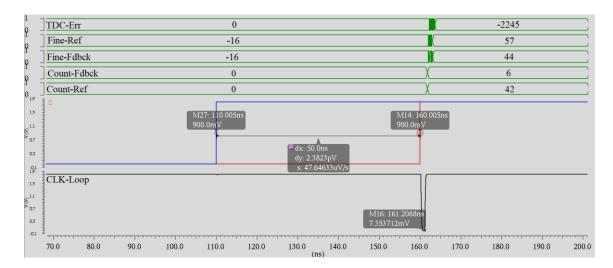

| 4.1.1.          | 50 ns time difference between Reference and Feedback clocks    | 57  |

| 4.1.2.          | -50 ns time difference between Reference and Feedback clocks   | 58  |

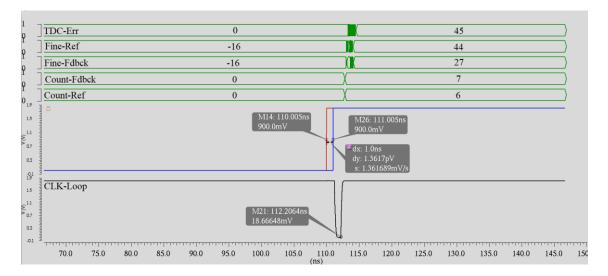

| 4.1.3.          | 1 ns time difference between Reference and Feedback clocks     | 59  |

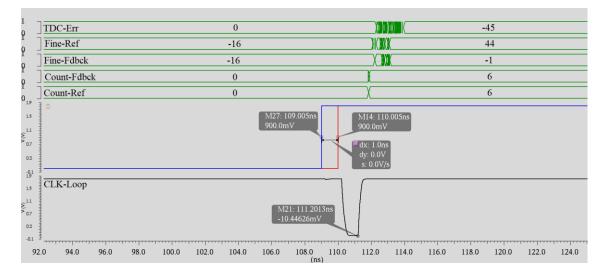

| 4.1.4.          | -1 ns time difference between Reference and Feedback clocks    | 60  |

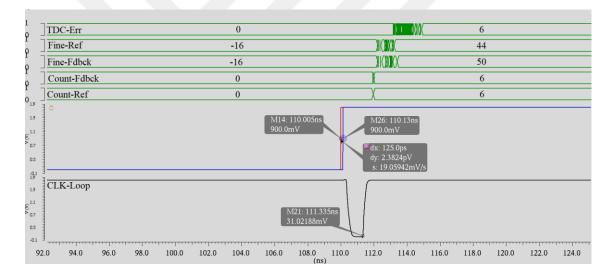

| 4.1.5.          | 0.125 ns time difference between Reference and Feedback clocks | 61  |

| 4.1.6.          | 0.102 ns time difference between Reference and Feedback clocks | 62  |

| 4.2. Peri       | odic Test Results                                              | 64  |

| 4.2.1.          | Periodic Test results for 50-49 ns input signals               | 65  |

| 4.2.2.          | Periodic Test results for 50-47 ns input signals               | 67  |

| 4.2.3.          | Periodic Test results for 50-43 ns input signals               | 68  |

| 4.3. PV7        | C (Supply Voltage and Temperature Dependency)                  | 69  |

| 4.4. Lay        | outs                                                           |     |

| 4.4.1.          | Layout of the Multi-Input Inverter                             |     |

| 4.4.2.          | Layout of the Ring Oscillator                                  |     |

| 4.4.3.          | Layout of the Frequency Detector                               |     |

| 4.4.4.          | Layout of the Phase-Frequency Detector                         |     |

| 4.4.5.          | Layout of the Digital Modules                                  |     |

| 4.4.6.          | Layout of the Top Module                                       |     |

|                 | nber of Gates and Area Reports                                 |     |

|                 | rent consumption of the Ring Oscillator and the overall TDC    |     |

|                 | ntization noise calculation of the overall TDC                 |     |

|                 | USIONS AND FUTURE WORK                                         |     |

|                 | РНҮ                                                            |     |

|                 | A                                                              |     |

| CURRICUL        | UM VITAE                                                       | 100 |

# LIST OF FIGURES

| Figure 2.1: Transition from Analog PLL to Digital PLL                           | 8  |

|---------------------------------------------------------------------------------|----|

| Figure 2.2: Blocks of Analog PLL                                                | 10 |

| Figure 2.3: Analog based Phase Detector                                         | 11 |

| Figure 2.4: Third Order Analog Loop Filter                                      |    |

| Figure 2.5: Voltage Controlled Oscillator Schematic                             | 13 |

| Figure 2.6: D-FlipFlop Based Frequency Divider                                  | 14 |

| Figure 2.7: Digital Phase Detector                                              | 15 |

| Figure 2.8: Block Diagram of Digital Loop Filter.                               | 16 |

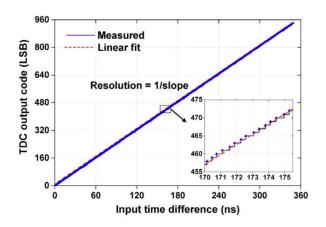

| Figure 2.9: Linearity and Resolution graph of TDC                               | 18 |

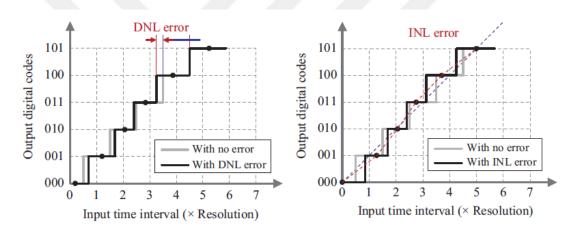

| Figure 2.10: a) DNL of TDC, b) INL of TDC                                       | 20 |

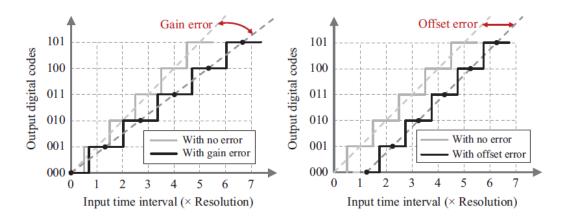

| Figure 2.11: a) Gain error graph b) Offset error graph of TDC                   | 21 |

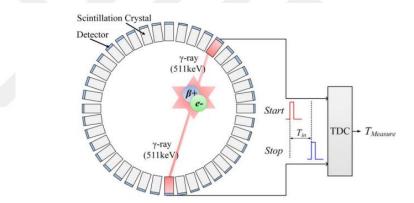

| Figure 2.12: Time-to-Digital Converter in PET Systems                           |    |

| Figure 2.13: TDCs in LiDAR applications                                         | 24 |

| Figure 2.14: Working principle of TDCs.                                         | 25 |

| Figure 2.15: Counter-based TDC architecture                                     | 26 |

| Figure 2.16: Working principle of time-based Analog-to-Digital converter        | 27 |

| Figure 2.17: ADC based TDC topology                                             |    |

| Figure 2.18: Buffer-based Flash TDC                                             | 29 |

| Figure 2.19: Vernier TDC architecture                                           | 30 |

| Figure 2.20: Common Ring Oscillator topology.                                   | 31 |

| Figure 2.21: Ring Oscillator based TDC.                                         | 32 |

| Figure 2.22: Vernier Ring Oscillator based TDC Topology                         |    |

| Figure 2.23: 2 Input inverter configuration                                     |    |

| Figure 2.24: 11 Phases multipath Ring Oscillator.                               | 34 |

| Figure 2.25: Alternative topology for Multi-Input Inverter                      | 34 |

| Figure 2.26: Gated Ring Oscillator with Nand gate                               | 35 |

| Figure 2.27: Gating Ring Oscillator with Multiplexer                            | 36 |

| Figure 2.28: First order noise shaping effect of Ring Oscillator.               | 36 |

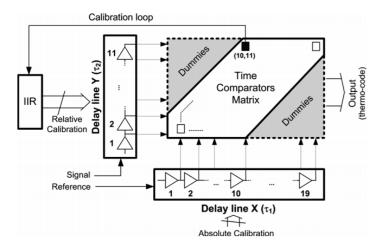

| Figure 2.29: 2D Vernier TDC topology                                            | 37 |

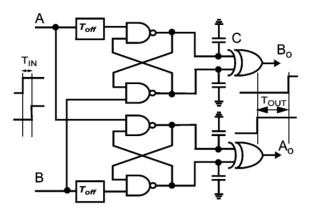

| Figure 2.30: SR Latch-based Time Amplificator circuit                           | 38 |

| Figure 2.31: Circuit Diagram of Multi-Step TDC                                  | 39 |

| Figure 2.32: Tuned-TDL structure in FPGA-based TDC                              |    |

| Figure 2.33: Algorithmic TDC architecture.                                      | 41 |

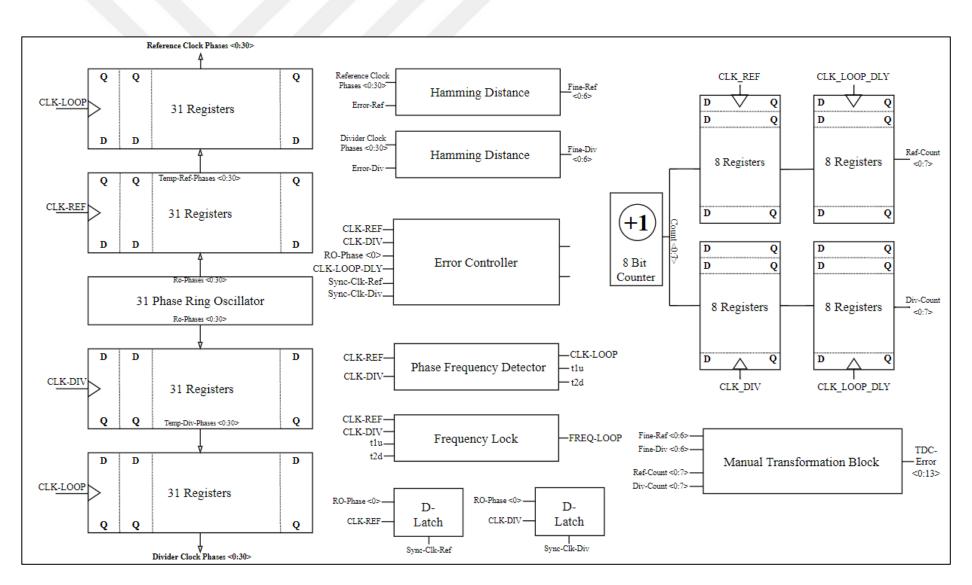

| Figure 3.1: Overall architecture of the proposed TDC                            |    |

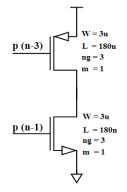

| Figure 3.2: Transistor sizes of Ring Oscillator's inverters.                    |    |

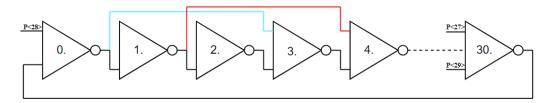

| Figure 3.3: Multipath Ring Oscillator architecture.                             | 45 |

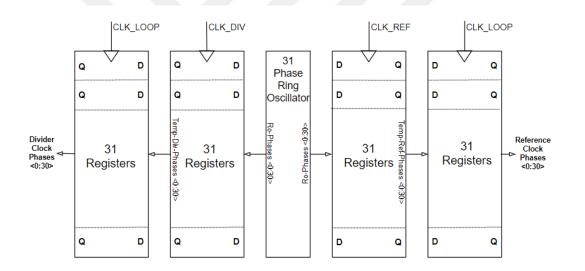

| Figure 3.4: Block diagram of the D-Flipflop array of ring oscillator phases     | 46 |

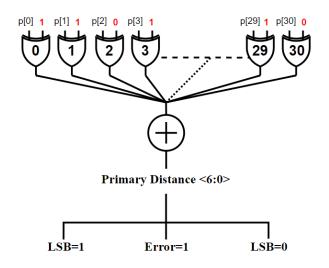

| Figure 3.5: Working principle of the Hamming Distance block                     | 48 |

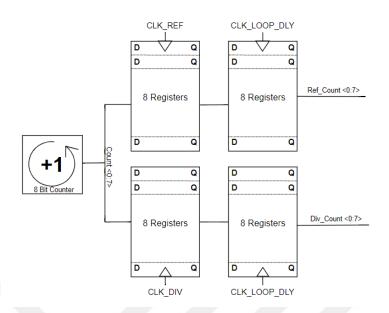

| Figure 3.6: Block diagram of the D-Flipflop array of counter outputs            | 49 |

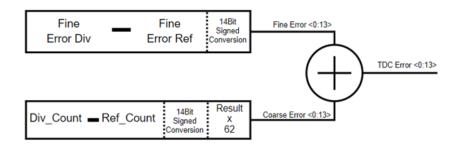

| Figure 3.7: Working principle of Manual Transformation Block                    | 50 |

| Figure 3.8: Block Diagram of the Phase Frequency Detector.                      | 51 |

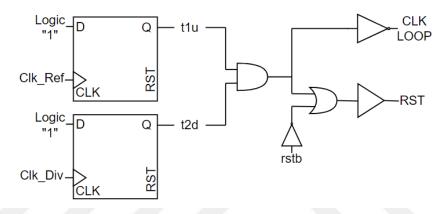

| Figure 3.9: Example output for the PFD module                                   |    |

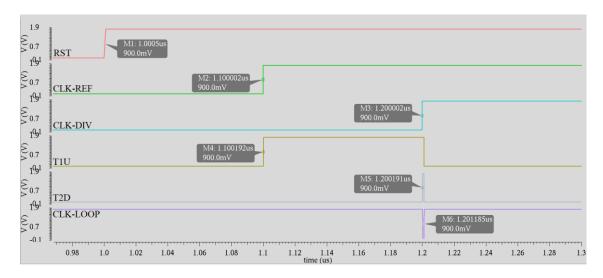

| Figure 3.10: Block diagram of the Frequency Lock module                         |    |

| Figure 3.11: Example output for the Frequency Lock module                       |    |

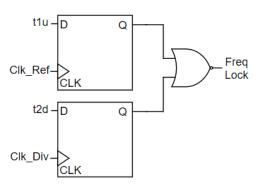

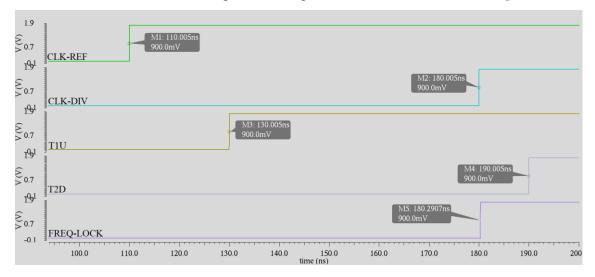

| Figure 3.12: Block diagram of the Error Controller modules                      |    |

| Figure 4.1: 14 <sup>th</sup> and 16 <sup>th</sup> phases of the ring oscillator |    |

| Figure 4.2: Propagation delay between phases.                                   |    |

| Figure 4.3: TDC phase error measurement for 50 ns time difference               |    |

| Figure 4.4: TDC phase error measurement for -50 ns time difference.             | 59 |

| Figure 4.5: TDC phase error measurement for 1 ns time difference                 | 60 |

|----------------------------------------------------------------------------------|----|

| Figure 4.6: TDC phase error measurement for -1 ns time difference.               | 60 |

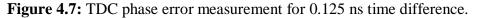

| Figure 4.7: TDC phase error measurement for 0.125 ns time difference             | 61 |

| Figure 4.8: TDC phase error measurement for 0.102 ns time difference             | 62 |

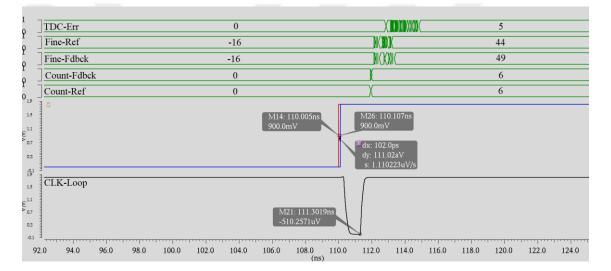

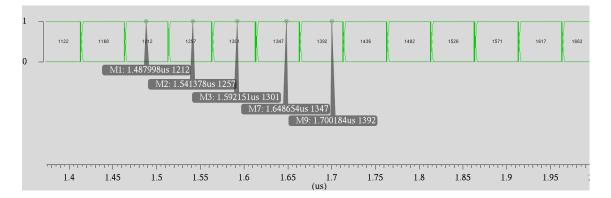

| Figure 4.9: Periodic test results for signals with 49-50 ns periods.             | 65 |

| Figure 4.10: Zoomed version of the 49-50 ns periodic measurement                 | 66 |

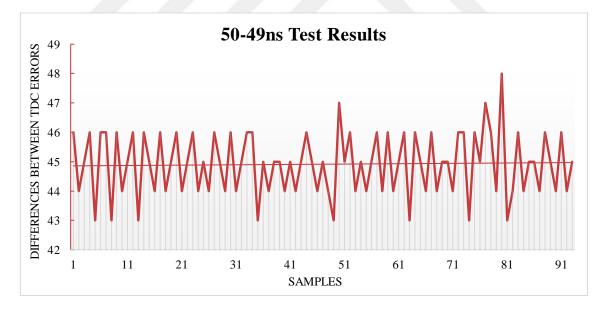

| Figure 4.11: Differences between each successive step for signals with a 50-49 n | IS |

| period                                                                           | 66 |

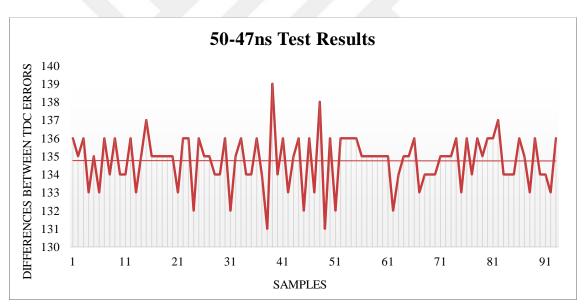

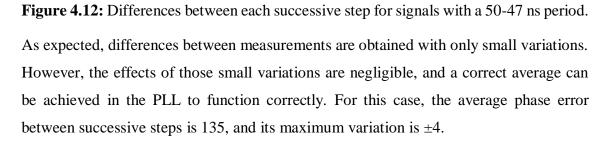

| Figure 4.12: Differences between each successive step for signals with a 50-47 n | IS |

| period                                                                           | 67 |

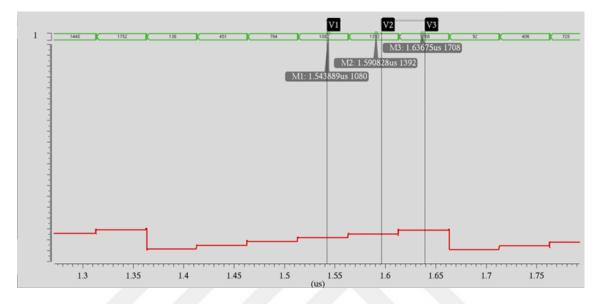

| Figure 4.13: Zoomed version of the 43-50 ns periodic measurement                 | 68 |

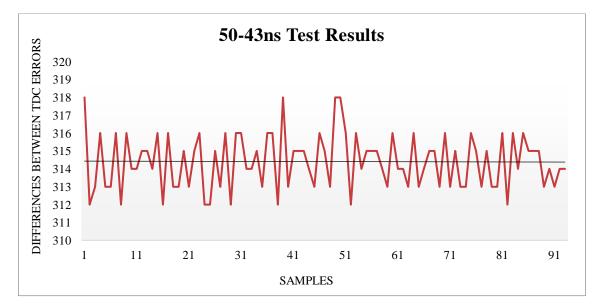

| Figure 4.14: Differences between each successive step for signals with a 50-43 n | IS |

| period                                                                           | 68 |

| Figure 4.15: Layout of the Multi-input Inverter.                                 | 74 |

| Figure 4.16: Layout of the Ring Oscillator                                       | 75 |

| Figure 4.17: Layout of the Frequency Lock module                                 | 75 |

| Figure 4.18: Layout of the Phase Frequency Detector                              | 76 |

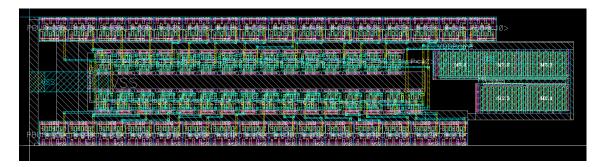

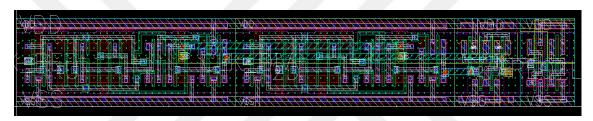

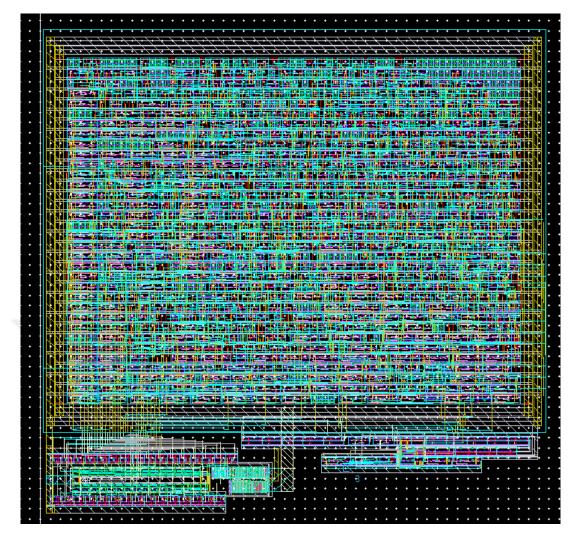

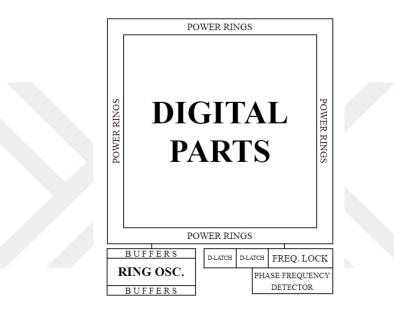

| Figure 4.19: Layout of the Digital Module                                        |    |

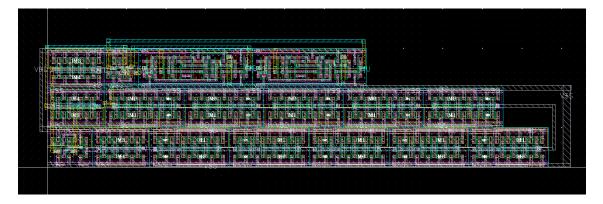

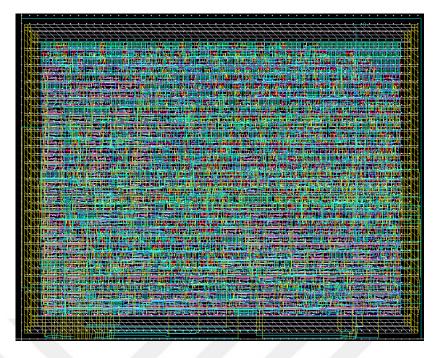

| Figure 4.20: Layout of the Top Module.                                           |    |

| Figure 4.21: Structure of the top module's layout                                | 79 |

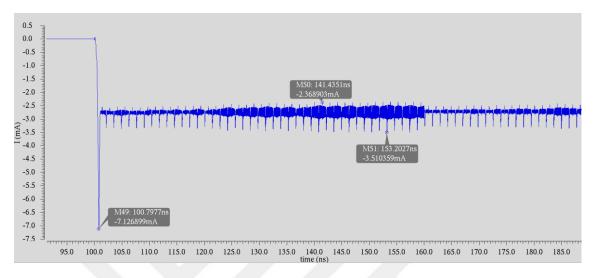

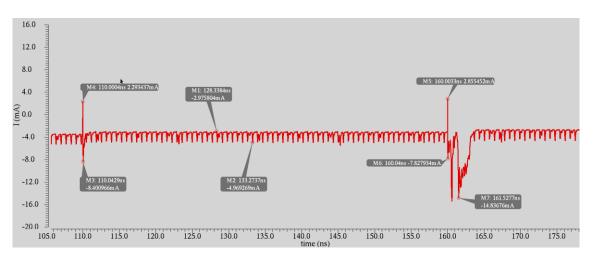

| Figure 4.22: Current consumption of the Ring Oscillator                          | 81 |

| Figure 4.23: Current consumption of the overall TDC.                             | 81 |

# LIST OF TABLES

| 50 |

|----|

| () |

| 63 |

| 69 |

| 70 |

| 71 |

| 72 |

| 72 |

| 80 |

| 80 |

| 82 |

|    |

# LIST OF SYMBOLS

- μ Ω : Micro

- : Resistance

- : Frequency : Hertz f Hz

# ABBREVIATIONS

| DII   |                                              |

|-------|----------------------------------------------|

| PLL   | : Phase-Locked Loop                          |

| TDC   | : Time to Digital Converter                  |

| PET   | : Positron Emission Tomography               |

| INL   | : Integral Nonlinearity                      |

| DNL   | : Differential Nonlinearity                  |

| TOF   | : Time of Flight                             |

| FLIM  | : Fluorescence Lifetime Imaging              |

| TOFMS | : Basics of Time-of-Flight Mass Spectrometry |

| LiDAR | : Light Detection and Ranging                |

| VCO   | : Voltage Controlled Oscillator              |

| PD    | : Phase Detector                             |

| PFD   | : Phase Frequency Detector                   |

| DCO   | : Digitally Controlled Oscillator            |

| RO    | : Ring Oscillator                            |

| DAC   | : Digital to Analog Converter                |

| ADC   | : Analog to Digital Converter                |

| ECG   | : Electrocardiogram                          |

| SSCG  | : Spread Spectrum Clock Generation           |

| ADPLL | : All Digital Phase-Locked Loop              |

| DPLL  | : Digital Phase-Locked Loop                  |

| SPLL  | : Software Phase-Locked Loop                 |

| RF    | : Radio Frequency                            |

| FPGA  | : Field Programmable Gate Array              |

| AI    | : Artificial Intelligence                    |

| SAR   | : Successive Approximation                   |

| ТА    | : Time Amplifier                             |

| NMOS  | : Negative-Channel Metal Oxide Semiconductor |

| PMOS  | : Positive-Channel Metal Oxide Semiconductor |

| ASCI  | : Application Specific Integrated Circuit    |

| DSP   | : Digital Signal Processing                  |

| MAC   | : Multiply and Accumulate                    |

| PVT   | : Process, Voltage and Temperature           |

|       |                                              |

# TÜM DİJİTAL FAZ KİLİTLEMELİ DÖNGÜLER İÇİN YÜKSEK ÇÖZÜNÜRLÜKLÜ ZAMANDAN DİJİTALE DÖNÜŞTÜRÜCÜ TASARIMI

# ÖZET

#### Tamer Eren

#### Elektrik-Elektronik Mühendisliği ve Siber Sistemler, Yüksek Lisans

#### Tez Danışmanı: Doç. Dr. Hakan Doğan

#### Eş Danışman: Yrd. Doç. Dr. Mustafa Aktan

#### Haziran, 2021

Faz kilitli döngüler (çevrimler), sadece iletişim devreleri için değil, biyomedikal ve bilgisayar bilimleri gibi diğer alanlarda da kullanılan en önemli modüllerden biridir. Analog, Dijital ve Yazılım tabanlı gibi birçok faz kilitli döngü türü mevcuttur ve bu türlerin birbirlerine göre avantaj ve dezavantajları vardır. Tüm Dijital faz kilitli döngüler, programlanabilirlik ve maliyet verimliliği gibi onları diğerlerinden ayıran birçok önemli özelliğe sahiptir. Topolojiden bağımsız olarak, tüm FKÇ' ler, frekansı giriş sinyalleri arasındaki faz veya zaman farkıyla orantılı olan bir çıkış sinyali sentezlemektedir. Fazlar arası uyum sağlandığında FKÇ "kilitli duruma" girer. Başka bir deyişle, çıkış sinyalinin frekansı giriş sinyali ile aynı olur. Faz kilitleme işleminin ilk adımı, Referans ve Geri Besleme sinyalleri olarak bilinen gelen sinyaller arasındaki zaman mesafesini ölçmektir. Farklı FKC türleri, faz farkını ölçmek için farklı alt bloklar kullanır. Dijital alanın avantajlarından kapsamlı bir şekilde yararlanmak için Tüm Dijital Faz Kilitli Döngüler, gelen sinvallerin fazlarını zamana dönüştürür ve bilinen referans açısından varış süreleri arasındaki farkı hesaplar. Bu tezde, 180nm XFAB teknolojisinde 22.18 ps çözünürlüğe sahip hibrit bir zamandan dijitale dönüştürücü tasarlanmıştır. Genel çalışma prensibi, ince ve kaba ölçüm olarak iki kısma ayrılmıştır. Daha sonra Verilog 'da ilk önce üst modül doğrulanmış ve ardından davranışsal Verilog kodları, RC sentez aracı ile "kapı düzeyi" kodlara dönüştürülmüştür. Model Sim'de öncü sonuçlar alındıktan sonra, prototipin şematik seviyesi, önceden tasarlanmış bir Standart Hücre kütüphanesi ile Cadence Virtuoso yazılımında sentezlenmiştir. Hata ölçümü sırasında 1,8 V besleme gerilimi kullanılarak, ortalama akım tüketimi 3.9 mA olarak elde edilmiştir. Fonksiyonel ve periyodik testlerden sonra, önerilen dönüştürücü, ±%10 besleme gerilimi değişimi ile köşe simülasyonlarında test edilmiştir. Ayrıca -200 °C 'den 85 °C 'ye kadar farklı sıcaklıklar için aynı testler tekrar edilmiştir. Tüm bu simülasyonlar başarıyla tamamlandığında, önerilen TDC'nin serimi 0.057 mm<sup>2</sup> alan kapsayacak şekilde tasarlanmış ve sonuç Mentor Calibre ile doğrulanmıştır. Son adım olarak, parazitlerin etkilerini gözlemlemek için serim-sonrası parazitik ekstraksiyon simülasyonu koşturulmuştur.

Anahtar sözcükler: TDC, ADPLL, Verilog.

# A HIGH-RESOLUTION TIME TO DIGITAL CONVERTER DESIGN FOR ALL DIGITAL PHASE-LOCKED LOOPS

#### ABSTRACT

#### Tamer Eren

#### MSc in Electrical, Electronics Engineering and Cyber Systems

#### Advisor: Assoc. Prof. Dr. Hakan Doğan

#### Co-Advisor: Assist. Prof. Dr. Mustafa Aktan

#### June, 2021

Phase-locked loops are one of the most significant modules that are used not only for communication circuits but also in other fields like biomedical and computer sciences. There are many types of PLLs such as Analog, Digital, and Software-based ones. However, they have advantages and disadvantages among each other, and All-Digital PLLs have many significant features like programmability and cost efficiency that make them stand out from the rest. Independent from the topology, all PLLs synthesize an output signal whose frequency is proportional to the phase or time difference between input signals. When the alignment between phases is achieved, PLL enters the "locked state". In other words, the frequency of the output signal becomes the same as the input signal. The first step of the phase-locking process is measuring the time distance between incoming signals which are known as Reference and Feedback signals. Different PLL types employ different subblocks to measure phase difference. Due to taking advantages of the digital domain extensively, All-Digital Phase-Locked Loops converts phases of the incoming signals to time and computes the difference between arrival times in terms of known reference. In this thesis, a hybrid time to digital converter with 22.18 ps resolution was designed in 180 nm XFAB technology. The overall working principle was divided into two parts as fine and coarse measurement. Then the top module was verified in Verilog first, and subsequently, behavioral Verilog codes were transformed to gate level ones by RC synthesis. After taking preliminary results in ModelSim, the schematic level of the prototype was synthesized in Cadence Virtuoso software with a pre-designed Standard Cell library. The average current consumption during the error measurement was obtained as 3.9 mA from a 1.8 V supply. After functional and periodic tests, the proposed TDC was tested across corners with  $\pm 10\%$  supply voltage variation. Moreover, the same tests were performed for different temperatures from -200 °C to 85 °C degrees. When all tests were completed successfully, the layout of the proposed TDC was done in a 0.057 mm<sup>2</sup> area and verified with Mentor Calibre. As the last step, parasitic extraction was performed from layout to observe the effects of parasitics in post-layout simulations.

Keywords: TDC, ADPLL, Verilog.

# **CHAPTER 1**

# **1. INTRODUCTION**

Phase-locked loops are one of the most significant modules that are employed in communication circuits as frequency synthesizers. They have many advantages in terms of programmability and cost among crystal oscillators.

Their working principle is based on measuring the phase difference between incoming signals and generating a new frequency whose frequency is proportional to this phase difference [1].

There are many different types of PLLs in literature, however, in this study, a Time-to-Digital converter was designed and proposed for All-Digital PLL.

In the digital domain, instead of utilizing phases of the incoming signals, their arrival times were processed to obtain time difference. TDCs catch these signals and compare their difference with a known reference to compute "phase error" at the end.

There are many methods in the literature for this evaluation process, which are mentioned in Chapter 2. However, the proposed method employs fine and coarse measurement techniques to get a 14-Bit phase error at the output.

The overall structure was built in Verilog first, then the behavioral Verilog codes were transformed to gate level in Cadence Virtuoso by RC synthesis tool. Standard cells that are prepared with 180 nm XFAB CMOS technology are employed for this transformation. Details about the working principle and the design architecture were shared in Chapter 3 and all the codes were given in Appendices. The schematic level of the proposed TDC is tested in different scenarios to investigate the functionality of the system. After all functional and periodic tests were completed successfully, the Place & Route process was initiated and the proposed layout was verified with DRC and LVS tests of Mentor Calibre. All the layouts, simulation results, and the PVT analyses were presented in Chapter 4. To

finalize the simulations, parasitic extraction was performed, and design was tested with parasitics to get the most realistic results. In addition to the individual testing, the proposed TDC was simulated inside a fully functional ADPLL to be sure about the functionality.

As a result, 22.18 ps resolution is achieved in typical corners with a 1.8V supply at room temperature. Moreover, the layout of the design is completed in a 0.057  $\text{mm}^2$  area.

# **CHAPTER 2**

# 2. THEORETICAL PART

# 2.1. Phase-Locked Loop Systems

A phase-locked loop (PLL) is a feedback control system that synthesizes a feedback signal with a certain phase to track the phase of a reference. In other words, PLL synchronizes a reference input signal to an output signal in terms of frequency and phase [1].

Phase-locked loops have various types in literature but the main principles behind them are the same. The first step is measuring the time difference between the incoming phase and the feedback phase, and creating an error signal. However, this error signal should be proportional to the amount of phase difference. The second step is making adjustments by changing a control signal with a charge pump and a filter in front of it. The final step is recovering the phase difference between signals by changing the VCO frequency [2].

PLL systems have various working states and ranges which can be listed as;

# Locked State

When the phases of the reference and the feedback clocks aligned, which means the phase error between them is "0", PLL enters into a locked state. In this state, phase and frequency error fluctuations should be very small.

# Hold-in Range

This range represents the largest frequency deviations that PLL ensures maintaining the locked state. The loop guarantees to re-achieve its locked position after tracking the new frequency.

# Pull-in Range

The Pull-in range states the locking interval of the PLL with an arbitrary initial phase and frequency. The locking process can be long but eventually, PLL frequency becomes stable after tuning of VCO.

# Lock-in Range

When the PLL is initially locked, this range covers the frequencies that the system eventually locks again even if there are abrupt changes. This synchronization process can take a long time due to cycle slipping [3].

Phase-locked loops are generally utilized in radios, telecommunication, computers, and other microelectronic applications. The first idea of the PLL comes around the 1920s while trying to achieve resonance between two oscillators.

In 1919, William Henry Eccles emphasized that if two distinct electronic oscillators are coupled to the same resonant circuit, they will eventually oscillate at the same frequency if they are originally tuned to oscillate at close frequencies. However, in 1923, Edward Victor Appleton developed a theory that explains the automatic synchronization between different oscillators [4].

In 1925, the automatic synchronization theory was realized by Professor David Robertson who employs an electromechanical synchronizer to regulate the striking of the Great George's bell. It compares the oscillation of the bell and the feedback signal which is coming from Greenwich Observatory.

Receivers in the analog televisions utilized PLLs, which provide locking to broadcast frequency, for synchronization of the horizontal and vertical pulses, until the late 1930s [5].

Phase-locked loop systems on a microchip were introduced by Signetics in 1969 [6]. After that, the area and power requirements of the PLLs were improved to get a higher frequency range and compact solutions. Today, there are PLLs with areas in the order of only hundreds of  $\mu$ m<sup>2</sup> used for industrial purposes.

# 2.1.1. Performance parameters of PLL

There are different parameters that determine the working range and the quality of the PLL systems. They are fundamental indicators of performance and can be traded according to the application.

• The most significant parameter of PLL is locking and capturing ranges, which can be also considered as the frequency band of PLL.

• Sensitivity is also another parameter that shows the quality of PLL. This property is directly related to the VCO block, and it shows the rate of change of created frequency with respect to unit increment in the error signal. The resolution which shows the closest distinguishable phase difference is also another important parameter for PLL and it determines unachievable phase differences, or in other terms offset error in locking condition.

- Locking time and transient response of the PLL also affect the function and the quality.

- Power consumption, the amplitude of the output, and area are some of the common considerations for all PLLs as well.

• Jitter and noise performance is also another significant parameter to obtain a clean frequency spectrum at the output [7].

To describe the working principle of the phase-locked loop systems, some properties should be explained extensively. One of the main properties that indicate the price and efficiency of the PLL is the level of sensitivity. The sensitivity or the minimum frequency steps of the VCO is important for fine-tuning the PLL. When the error output of the phase detector varies slightly, the frequency of the VCO should not change by a large amount. In addition to that, the frequency band of the VCO directly indicates the working range of the PLL, in other words, capturing range of the system.

Moreover, the resolution can be described as the closest measurable distance between rising edges of the reference and feedback clocks in the locked state. Phase detectors or TDC architectures are the main determinants of resolution in PLL systems [8]. Furthermore, phase error in the "locked state", in other words, the time difference between the phases of the input clocks is called static offset error which is inevitable. Even for very low operating frequencies, there will be some errors due to the non-zero

delay between the phases of clocks or delay lines. PLLs cannot resolve these differences because they are smaller than the resolution of the system.

In ideal circumstances, the static phase offset should be zero, which means, in lock condition reference and the feedback clocks have to be aligned. However, adjusting and lowering this static offset, which means increasing the resolution can solve jitter issues, and phase noise is the most common type of jitter observed in PLLs [9]. Jitter is almost inevitable for PLL systems and it is originated from the oscillators. The tracking jitter should be as low as possible to increase the performance of the PLL system. Phase noise can be minimized by the careful design of the sub-blocks of the PLL as well as by optimizing the overall top-level PLL system. Furthermore, sudden changes in the supply voltages, ground nets, or substrate noise affects jitter performance. Consequently, PLLs with higher noise rejection have better performance [10]. An injection or self-injection oscillator can be applied to obtain better phase noise in the VCO block of PLL [11].

### 2.1.2. Usage of PLLs

Phase-Locked Loops are generally used in processors, FPGAs, and radios for generating the system clock or the RF frequency. The main fields that use PLL are unsurprisingly electronics and communication because compatible demodulation of incoming signals with an internal signal is a fundamental requirement of these fields. Synchronization of the bits in digital communication is also another purpose of employing Phase-Locked Loops.

By employing PLLs, new frequencies can be synthesized which are multiple or the same with a reference frequency in the microchips. These new frequencies should meet the stability constraints of the reference clocks. Generating new frequencies with PLL in higher bands is also much cheaper than using high-frequency crystal oscillator solutions.

There are some other applications of PLLs such as frequency demodulation. If the output of the phase-locked loop is locking to a frequency modulated signal, the voltage-controlled oscillator should adjust itself to the instantaneous frequency of the input signal. VCO of the communication system controls its output via error signal and PLL should cover all the ranges of VCO as linear as possible [12].

The same procedure also applies to phase modulation as well. However, this time, the phase of the system is much more important and PLL should cover this phase range for successful demodulation [13].

In digital communication, instead of using an analog signal directly, digitally generated bits and symbols should be transmitted via carriers. Computers, routers, or any kind of transmitter-receiver pair uses PLL to catch and track carrier frequencies of these binary data which is shifted between two or more frequencies.

Amplitude demodulation can be another perspective for the usage of PLLs [14]. AM signal's carrier can be recovered in terms of phase and frequency by PLLs and generally, the phase of the recovered signal is obtained with a 90° degree phase shift. PLL-based amplitude modulation detector tends to have excellent selectivity and enhanced noise immunity due to the working range of the PLLs in specific bands around carrier frequencies that are also close to the output of VCO [15]. Phase-Locked Loops are also employed in a modulation part, where specific frequencies should be synthesized.

Other than communication systems, there are various applications that need a PLL for several purposes. For instance, microprocessors and computers need an internal system clock to process the data. Generally, crystal oscillators were employed to obtain the main frequency due to the high precision requirement. However, other frequencies, which are multiples of the main one, can be obtained via PLLs. Moreover, the multiplication constant can be quite large to obtain operating frequencies in the gigahertz band where the reference crystal is in the megahertz range [16].

Clock and data recovery is another application for the PLL systems. Basically, CDR extracts the received data stream which is coming from the receiver. In these types of systems, distortion can lead to loss of clock information, and PLL recovers or regenerate proper clocks [17]. In this case, the transition of the data should meet the frequency range of the PLL to be able to create or track frequencies.

Furthermore, one of the main implementations of the PLL is preventing or minimizing the effects of skewing in digital circuits. Skewing can be explained as different arrival times of the same clock to the input of different gates. If the delay causes a phase shift, this can lead to serious synchronization and timing problems in the overall system. The deskewing function of the PLL is employed to align these skewed clocks to the original input and match the phases [18]. For this kind of application, the delay-locked loop is much more applicable rather than conventional phase-locked loops. DLL creates a delay line and compares the phase of the input and reference signals. After filtering of mismatch

between these signals, the result is used in the VCO and the phase of the control signal is adjusted.

In addition to the fields represented above, PLLs are employed for the synchronization of video signals [19], boosting the microcontroller's operation clocks [20]. Also, in Biomedical, they are utilized in surface-tip relations of Atomic Microscopy [21], reduction of electromagnetic interference in ECG systems [22], and clock generation for implantable biomedical devices [23].

# 2.1.3. Types of Phase-Locked Loops

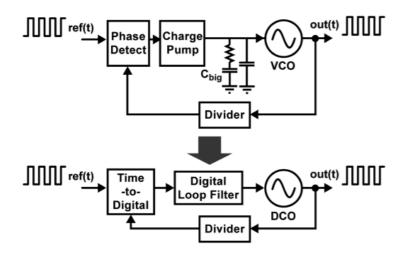

Almost every single application requires different properties and specs from phase-locked loops and these different requirements can be met with various types of PLLs. Analog applications require relatively low phase-noise phase-locked loops. For instance, radio receivers and transmitters could use Analog PLL systems. Moreover, the combination of the analog and digital components (blocks) creates a digital phase-locked loop (DPLL), and if all modules in the PLL are synthesized digitally, it becomes an all-digital phase-locked loop (ADPLL). However, for software applications that are not designed physically, there are software phase-locked loop (SPLL) systems as well [24]. In **Figure 2.1**, differences between blocks of Analog and Digital PLL can be examined.

Figure 2.1: Transition from Analog PLL to Digital PLL [25].

Analog or Linear PLL (APLL)

Analog phase-locked loops employ phase detectors which are designed as an analog multiplier to detect incoming phases. Basically, it generates a product of two incoming signals to extract their phase correlations. The output of the phase detector acts as an error signal and directly feeds into a filter that smoothes the phase difference. At the output of the filter, a voltage-controlled oscillator generates an oscillation frequency as a function of the incoming filtered error value. The overall system uses the VCO output to generate feedback to reduce the difference between the two phases.

# Digital PLL (DPLL)

Digital phase-locked loops combine the function of analog PLLs with digital blocks. Instead of using an analog phase detector, flipflop and XOR-based digital blocks measure the phase difference between the incoming phases. Furthermore, a digital filter and a digitally controlled oscillator can be utilized in digital PLL.

# All digital PLL (ADPLL)

Without using any analog modules or submodules, every single function in the analog PLLs is mimicked via digitally synthesized modules. Time to digital converters are used rather than an analog phase detector, and filtering can be achieved digitally. Moreover, the result of the filter is used as a control input for the fine and coarse tuning of the digitally controlled oscillator. In the feedback loop, a frequency divider with a sigma-delta modulator can be utilized for generating the feedback signal.

# Software PLL (SPLL)

As an alternative to physical hardware, all the functions of phase-locked loops can be implemented via software. Software PLLs can be standalone modules as well, but they are also a good practicing method to solve functioning issues before synthesizing the circuit.

# 2.1.3.1. Analog PLL blocks

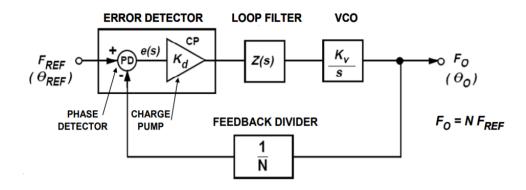

The function of the phase-locked loops is almost the same for every type of PLLs. On the other hand, the types of the blocks can be changed, and in **Figure 2.2**, the most common configuration of the Analog PLL blocks is shown.

Figure 2.2: Blocks of Analog PLL [26].

Phase detector or time to digital converter measures the phase or time difference between incoming signals to generate an error signal that is proportional to the phase difference. After low pass filtering of this error, voltage or digitally controlled oscillator generates a periodic clock. The frequency of this signal is controlled by the error signal, in other words, the output of the oscillator is also proportional to the phase difference between two signals. Furthermore, a feedback divider is implemented to facilitate the evaluation process in the phase detector which will be mentioned later.

# **Phase Detectors**

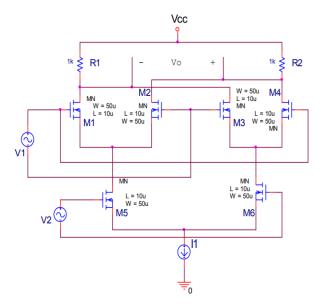

The phase detector takes in two signals at the input side and generates an error signal which demonstrates the difference between the 2 phases. These phases are known as reference input and feedback from the voltage-controlled oscillator. In each measurement, the output of the detector feeds a low-pass filter to eventually control the output frequency of VCO. The sensitivity of the phase detector is the most significant property for this module and PLL loops continue until the phase error becomes "0" [27]. Phase detectors in analog PLLs are designed at the transistor level with a multiplexer idea. In **Figure 2.3**, an example for a transistor-level analog phase detector is demonstrated.

Figure 2.3: Analog based Phase Detector [28].

Frequencies of the input signals were multiplied and compared to get two different frequencies in output which represents phase differences of incoming signals.

A conventional solution to ensure stability in phase error signal is using a charge pump, which is fed by the output of the phase detector. It regulates voltages which will be used as an input of the low-pass filter, using charge pumped into a capacitive-energy storage element [29]. Charge pumps guarantee high-efficiency solutions for low output current applications. Also, they provide constant and stable output with varying error input.

# **Analog Filter**

Almost all types of PLLs employ a loop filter that shows low-pass characteristics for regulating the error signal from the PD.

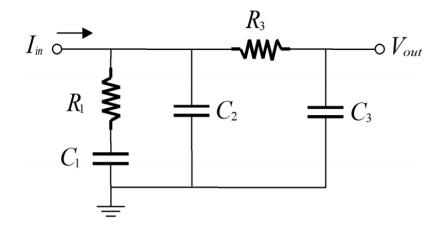

The most significant function of this loop filter is adjusting the loop dynamics, which are bandwidth, gain, and stability. Also, the order of the filter is important and directly affects the performance of the PLL. The schematic of a 3<sup>rd</sup> order PLL filter commonly used in PLLs is presented in **Figure 2.4**. The bandwidth of the PLL is determined by the filter and it also regulates the lock range and lock speed of the overall loop. Moreover, the filter ensures the stability of the systems when it is disturbed due to sudden interferences and disruptions at reference and feedback clocks.

Figure 2.4: Third Order Analog Loop Filter[30].

The second property of the filter is adjusting the amplitude of the incoming error signal. A filter can be utilized to increase the amplitude as well as to attenuate it. Gain and phase margins of the PLL are the most important design parameters for this regulation [31]. A low pass filter is also employed to limit the amount of ripple on the VCO control voltage. Also, filtering is significant to ensure the lock condition and reducing the number of spurs at the output. Phase noise is another important parameter for filter design that can affect the design parameters of the filter.

# **Voltage Controlled Oscillator**

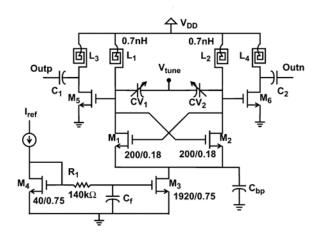

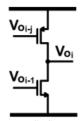

The Voltage Controlled Oscillator is the main component of the PLL and is controlled by the loop to generate the desired frequency. The first and the most significant property of this block is the frequency range. Voltage-controlled oscillators adjust their outputs via an incoming control signal. These adjustments and the generation of the oscillation frequency can be realized in various ways. One of the most common methods is taking advantage of the resonance between an inductor and varactor that changes its capacitance with the change in control voltage. This type of VCO is called the LC oscillator and **Figure 2.5** shows the schematic for an NMOS-Only LC oscillator. Varactors can be obtained via a reverse-biased diode which is controlled by the control voltage and they have wide range capacitance ratios [32]. In addition to them, there are inverter-delay-based ring oscillators as well [33].

Generally, the frequency of oscillation should be stable as possible regardless of the type of the VCO.

Figure 2.5: Voltage Controlled Oscillator Schematic [34].

After measuring the phase difference in the phase detector, the obtained error signal indicates any required increment or decrement in the oscillation frequency of the VCO. For instance, if the output frequency of the VCO signal is lower than the desired value, which means the phase of the VCO falls behind the phase of the reference, the error will affect control voltage positively to increase the VCO frequency and vice-versa e.g., if the phase of the reference is behind the feedback clock, then the frequency of the VCO is lowered.

# **Feedback Divider**

The adjustable frequency divider is another common block that is used in the feedback line of the PLLs. They use the output of the VCO to generate a new frequency which is a rational multiple of the newly synthesized clock. Thanks to the divider in the loop, the previously generated clock can be varied into many frequencies which is not possible by using the VCO only.

The range of division ratio is the most significant parameter in the divider design. However, rational multiples of the main frequency can be achieved easily by using registers such as given in **Figure 2.6**.

Figure 2.6: D flip-flop based Frequency Divider [35].

On the other hand, dividing the feedback clock with fractional numbers is more cumbersome than the normal division. These kinds of applications require multi-modulus divider blocks to determine the division ratio of the signal. Sigma delta modulators with various orders are generally used for fractional division. The main principle behind them is to randomly vary the division ratio to achieve an average divide ratio [36].

Furthermore, working in low frequencies eases the speed requirements significantly, hence some PLLs utilize a high-speed pre-scaler to scale the high-frequency VCO output to more manageable lower frequencies.

# 2.1.3.2. Digital and All-Digital PLL blocks

Even though All-Digital phase-locked loop systems have the same function as Analog PLLs, there are significant differences in terms of performance and building blocks between them. First of all, All-Digital PLLs tend to have a smaller locking time than analog devices at the same frequency band [37]. Moreover, All-Digital phase lock loops maintain their lock conditions even for sudden changes in the reference clock in terms of phase and frequency. In other words, losing the locking state is much harder than the analog PLL systems. Even they can reject noise and jitter more successfully than analog PLLs, their size is bigger because of the additional adder and divider blocks. However, the integrity of the design highly depends on the process, and the sizes of the filters are the main indicators for the size of the overall architecture. On the other hand, in terms of cost and complexity of the design, analog PLLs can be a better solution rather than digital ones. Furthermore, All-Digital PLLs can be utilized in high-frequency RF synthesizers with high resolution and fast settling [38].

After the development of DCO, researchers achieved precise frequencies that can be controlled via reference digital words. There besides, designing the smaller and faster digital gates facilitated the transition from the analog to the digital domain. Eventually, in the late 1980s, the All-Digital PLL idea was started to grow, and in the 2010s field-programmable array-based PLL was proposed [39], [40].

# **Phase Detectors – TDC**

Before using "All-Digital PLLs", various types of digital modules are utilized as a detection of the phase in the "Digital PLLs". The easiest and most famous one is the simple XOR gate. When the signals have different levels, output automatically becomes logic 1 to show the unmatched regions. There are 2 main issues in XOR implementation. The first one is a lack of sensitivity at the edges of the signals and the second one is the inefficient measurement of difference. To calculate or understand the phase difference exactly, time at the logic 1 state of the output should be measured with a stable reference.

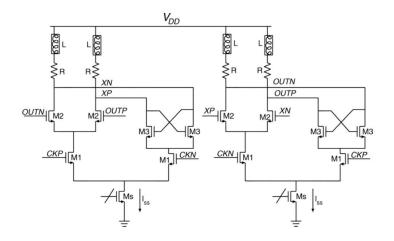

Also, J-K or D flip-flops can be utilized like in **Figure 2.7** to get an error signal that changes due to the phase error between reference and feedback clocks. However, again the main problem is dividing the overall error into fine and coarse parts which should be considered distinctly.

Figure 2.7: Digital Phase Detector [41].

Bang-bang architectures are another common type of phase detector that can be used in all-digital PLLs. Basically, it operates with D flip-flops for the detection of phase in "up" and "down" conditions [42].

When the transition from Digital PLL to All-Digital PLL is completed, phase detectors were transformed to the Time-to-digital converters which can hold the incoming phases

as a time substance and divide them by well-known coefficient. Design steps and all examples about TDCs will be presented in the next chapters.

# **Digital loop filter**

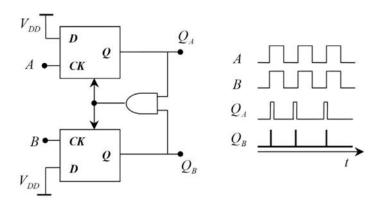

Without using any passive elements like resistors or capacitors, basic programmable integrators and delay elements are utilized for low pass filtering [43]. Functionality and programmability of the filter are designed by synthesizing it from VHDL or Verilog codes. **Figure 2.8** shows the block diagram of a digital low pass filter that is designed in this project. Regulation of the bandwidth and the gain is also much easier in digital filters and also the locking speed of the PLL system becomes adjustable via this approach.

Figure 2.8: Block Diagram of Digital Loop Filter.

# **Digitally Controlled Oscillators**

Instead of using a control voltage to regulate oscillation frequency, digitally controlled oscillators utilize incoming error bits to control oscillation. Simply, digitally controlled oscillators combine the function of VCO with the working principle of a DAC [44]. There are various types of DCOs that are designed to use be used in different frequency ranges. MOS Varactors and capacitor arrays are used to control the frequency of the DCO. Nevertheless, obtaining a stable frequency, and maintaining that specific point is the most significant specification for the DCO. A Digital feedback divider is employed after the DCO to divide the clock for comparison with the reference clock. Their functions and working principles are almost the same as the analog ones.

# 2.2. Time-to-Digital Converters

Time-to-digital converters are employed as phase detectors for all-digital phase-locked loop systems. Before phase-locked loop applications, TDCs have been utilized for more than 20 years in the applications of nuclear physics and biomedical where measurement of precise time-interval is required [45]. The first step of the time to digital converter is catching the rising or falling edges of 2 clocks and producing an error that will be proportional to the "time" difference between edges of the inputs. The most common field that embeds TDCs into the center of their system is communication electronics. However, other fields such as logic analyzers and digital scopes are also important applications of TDCs. Furthermore, almost every single time-of-flight measurement requires specific TDCs for the calculation of time intervals.

Analog circuits should be highly linear and precise to process the data which is placed into the envelope (amplitude) of the signals. Conversion and digitization of this data into the time domain facilitates signal processing and also eases the design of the overall systems. For this kind of application time-to digital or digital-to-time converters can be utilized. Moreover, TDCs can be used as a subsidiary element of ADCs for digitization purposes. The first example of a TDC was developed in the year 1942 by Bruno Rossi for the measurement of sub-atomic particle lifetimes [46]. It was designed as a time-to-amplitude converter, which charges a capacitor during the measurement of the two distinct events. On the other hand, until the end of the 1990s, analog signal processing in the time domain with TDCs has not become popular due to the micro-scale-based transistor technologies [47].

In terms of area, speed, and power, digital circuits benefit from the edge on improvements of transistor sizes, and in the deep sub-micrometer domain, analog and digital circuits started to use the time domain measurements for signal processing. In the first examples of TDCs, the resolution of the time interval between reference and feedback measurements has required nanosecond levels but recent developments demonstrate that synchronization of the clocks can be achieved in femtosecond levels. As a result, transmitters and receivers employ all-digital phase-locked loops (ADPLLs) which digitize the phase shift between clocks by TDCs.

#### 2.2.1. Performance parameters of Time-to-Digital conversion

Although all TDCs perform the same function, some performance parameters vary depending on the application. In other words, time to digital converters digitize or quantize the time difference between inputs, but the required speed, area, and bandwidth of the operation can change. Some of the parameters should be explained in detail to understand the working principle and developing process of the TDC in this study. Principally, the performance parameters of TDCs are close to ADCs but they have some unique characteristics that are due to time conversion.

#### 2.2.1.1. Resolution

The resolution of a TDC is the most fundamental and significant parameter that describes the smallest distinguishable time difference value that the converter can achieve. Recent CMOS processes detect time differences in femtosecond levels. Even though it is negligible in state-of-the-art solutions, finite resolution causes quantization noise, which can be considered as the static offset. If the system employs a ring oscillator to measure the time difference, the delay between each element indicates the resolution. Essentially, as with the LSB of an ADC, the resolution is a step width in the quantization characteristics of a TDC, which can also be explained as the range of continuous-time inputs that are transformed to the same digital word [45]. Actually, the resolution is an intangible term, but it can be examined in **Figure 2.9** conceptually.

Figure 2.9: Linearity and Resolution graph of TDC [48].

#### **2.2.1.2.** Output bits

The number of the output bits (NoB) determines the maximum time difference that the TDC can resolve. The output of the TDC goes through a filter and indirectly regulates the oscillation of the VCO. In other words, the number of output bits controls the detectable

range of the PLL. Using an adequate number of bits is important to determine the locking range of the PLL as well as power consumptions [49].

Essentially, the dynamic range can also be explained as the maximum time difference that TDC can measure. Above that level, TDC gives the same results for all differences, in other words, it enters the saturation region. In some of the applications, the dynamic range determines the maximum measurable time difference. For instance, in LiDar implementations, the detectable longest distance depends on the dynamic range of the system. Dynamic range can be increased by using more bits in the error signal. However, area and power limitations prevent the usage of long digital words in the output. Moreover, filter or charge pump design is directly related to the length of output error. In other words, making arbitrary changes may not be possible when all the design aspects are considered. The correct way to determine the dynamic range of the TDC depends on the application it is designed for. For PLLs, it directly depends on the reference signal and the oscillation frequency of the VCO. On the other hand, in time-of-flight PET, the TDC should cover all the possible annihilation points, which are the source points for gamma emissions in a specific range of detector rings [50].

### 2.2.1.3. Linearity and non-linearity

Principally, a time-to-digital converter is a subcategory of an analog to digital converter and like all the other data converters, one of the most important properties is the linearity of the operation. For 50 ps resolution, 1 ns phase difference between two clocks should give 20 as a "phase error" output in conformity with linearity property. Similarly, the 2 ns phase difference should give 40. The linearity property of the TDC can be affected by phase noise, device mismatches, and parasitic capacitances. Moreover, the delay between ring oscillator phases can cause nonlinearity. There are various ways to improve the linearity of TDCs and one of them is employing less amount of delay between phases of the ring oscillator [51]. If delays between buffers or inverters are not equal to each other, this phenomenon can cause an unbalanced calculation of the phase error.

The linearity stipulations of a PLL can be categorized as the dynamic performance of a system and DC accuracy [49].

In an all-digital phase-locked loop system, phases of the incoming signals are almost time-invariant at the locked state. In other words, during the locked state, the input of the TDC does not change in time. On the other hand, because of the nonlinear characteristics of data transformation, harmonic distortions may occur as in any converter. These distortions are observed as spurious tones in the output spectrum, and they can even be obtained in the locked state. Besides, not only TDCs but also the overall PLL systems can suffer from these nonlinearities. Due to these reasons, possible nonlinearities should be designated before any implementation. Unfortunately, TDC modules should have finite resolutions in the picosecond levels, and this behavior results in extra quantization noise which can affect the output spectrum of the PLL negatively [52]. However, increasing the resolution still important because the effects of quantization noise become negligible if it is smaller than the phase noise of DCO.

Any type of nonlinearity can be detected from the monotonicity and integral nonlinearity (INL) graphs [49] as is shown in **Figure 2.10**.

Figure 2.10: a) DNL of TDC, b) INL of TDC [49].

Integrated Non-Linearity (INL) is the difference between the expected and measured output values for a specific input code. Also, there is another important linearity metric for data converters given as Differential Non-Linearity (DNL), and it demonstrates the amount of variation between the two subsequent digital outputs from the ideal step. Principally, INL is the summation of the DNLs for the overall word as is shown in equation **2.1**.

$$INL_n = \sum_{i=0}^n DNL_i \tag{2.1}$$

# **2.2.1.4.** DC accuracy

DC accuracy of a TDC states the worst-case variation of the transfer function from a linear response in terms of gain and offset error.

Transfer function:

The relation between the time difference between incoming clocks, and the output error signal can be presented with a transfer curve of the time-to-digital converter.

Gain error:

The difference between the ideal and actual transfer curves of a TDC in a time scale is known as a gain error. In other words, the maximum time difference of the clocks will be represented with fewer bits, and it will change the slope of the transfer curve.

Offset error:

TDCs should not generate an error signal at the output without any input clock or 0 phase difference conditions. This problem can lead to LSB shifting in the transfer curve and also affects the frequency of the oscillation in VCO. An example graph for the offset and gain error is presented in **Figure 2.11**.

Figure 2.11: a) Gain error graph b) Offset error graph of TDC [49].

# 2.2.1.5. Power and area

Like all the other electronic components, the ultimate requirement for TDCs is achieving the best performance with less power in a smaller area. The development of smaller transistor feature sizes that also minimize the power consumption is the first key to meet optimum solutions. Furthermore, the function of the TDC can be developed with an architecture that minimizes the area of the solution on a chip.

Nonetheless, any delay line-based oscillator that is used as an internal reference will consume a big portion of the power, and there are various design methodologies to reduce the power consumption of these elements [53]. However, if TDC is synthesized via a design synthesis tool, standard cells with low power dissipation should be utilized.

# **2.2.1.6.** Dead time and counting rate

The dead time of a time to digital converter is one of the most significant parameters that show the quality and the performance of the system. It can be explained as the required time to complete digitization of the single time difference. Each application demands different dead intervals to achieve successful digitization. For example, high-speed machine learning and image processing applications require fast samplers to recreate images. Moreover, positron emission tomography (PET) also needs small latency between samples to create an image of a tissue or body. For these implementations, TDCs with small dead time and large counting rates can be employed to increase the quality of the final product. State-of-the-art methods can achieve up to 7.5 ns dead time which is good enough for almost any application [54]. However, if the overall frequency of the system is increased, the dead time of the one-clock-cycle-based designs improves.

On the other hand, finite dead time is inevitable for systems that have a single calculation unit even if the time distance is very small. However, there are many approaches and design techniques to limit the dead time. Employing parallel calculation units in a single TDC architecture is one of the most famous solutions for dead time. The fundamental working principle is when one of the processors starts to measure the time difference, the other one waits for the new signal. In other words, while one of them is working, the other one stays in a hold mode, until a new signal arrives during the measurement process. Some of the interleaved topologies were proposed [55], [56] to reduce dead time and increase digitization rates.

# 2.2.2. Usage of TDCs

There are so many applications of TDCs which are outside of PLLs as well. Even though all previous examples are related to PLLs and time to digital converters and DTCs are the signature blocks for ADPLLs, TDCs can be utilized in the time interval measurements individually. Also, the phase-shifting process takes advantage of digital-to-time converters which can also be used as a time delay element.

Time to digital converters are utilized not only for communication or RF engineering but also in physics and biomedical devices. Positron Emission Tomography (PET) and Fluorescence Lifetime Imaging (FLIM) are good examples of TDC applications in medicine [45]. They use time of flight measurements, which are also the same as absorption time measurement techniques, to create a detailed image of the tissue. In PET systems the time difference between two opposing gamma-ray emissions, and the event signals can be measured with TDCs precisely [57].

Coincidence counters also utilize time-to-digital converters as time taggers. Simultaneous detection of subatomic materials within a microsecond level requires high-end counters and they use the time to digital converters to hold and measure the time difference between 2 particles, which are emitted from the same nucleus [58].

These counters have a significant role in quantum physics and biomedical imaging experiments for measuring the correlation of gamma-rays. In a PET scanner, gamma radiation from the destruction of the positron-electron pair was examined via detectors after a substance that can emit positrons is applied to a subject. The location of the subject organ or tissue can be found by counting the time between emission and detection. This time information is used for calculating the exact coordinates of the radio-tracer substance as well. TDC-PET combination given in **Figure 2.12** is employed to digitize gamma-ray pairs' times of flight times after detection [59].

Figure 2.12: Time-to-Digital Converter in PET Systems [45].

Spectrometry is another biomedical application where TDCs are commonly used. Distinguishing a substance that contains different materials can be a good definition for spectrometry. Because of the different masses and charges of ions, they can be classified with respect to their interactions with light. One of the most known spectrometry examples where TDCs are utilized is Time of Flight Mass Spectrometry (TOFMS) [60]. In TOFMS, after ionization of the molecules, they are accelerated until reaching the same kinetic energy and because of different masses, arrival times will vary for each substance. However, when the initial time is known, the difference between the starting point and the arrival time can be measured via TDC.

Time of flight tomography utilizes the same principle behind the TOFMSs, and they also employ TDCs for biomedical imaging. Moreover, fluorescence spectroscopy utilizes time to digital converters to successfully measure the decay time between light-excited substances. Each time difference pulse represents different molecules [61].

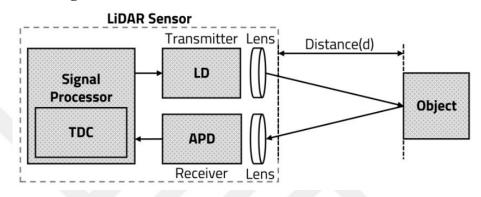

In laser imaging detection and ranging (LiDAR), the most important parameter to recreate an image is the time difference between the emission from the source and the arrival time of the reflected photons. The detection time between these signals is also utilized to measure the distance between target and source. TDC quantizes and digitizes this distance for further signal processing [62]. The detailed working principle of the LiDAR system is presented in **Figure 2.13**.

Figure 2.13: TDCs in LiDAR applications [63].

In the RF domain, because of the high frequencies, the required minimum detectable time interval should be smaller than the less sensitive applications. These kinds of applications expect high resolution from TDCs, and their design is more complicated than others.

A couple of picoseconds or even femtosecond resolutions can be utilized for these purposes. Also, the bandwidth of the TDC should be higher in RF applications and this requirement is directly related to the dynamic range of the TDC's output. More bits in the output mean that more space to represent bigger errors in time [64].

Furthermore, a successful TDC should be fast between the calculation of successive time differences. If a new time difference comes during calculations, the overall PLL loop can be broken, and the system gives erroneous results which can lead to misregulation of the oscillation frequency of the VCO. The time digitization operation needs to be as linear as possible to ensure each digital step represents the same time difference. This behavior is extra important in the RF domain because even small amounts of miscalculation of the error can cause bigger problems in the system. Actually, independent of the frequency range, all TDCs should have a wideband working range, high resolution, and fast operation specs between each successive (periodic) time conversion process [65].

Rather than using signal processing, some of the deep learning techniques can be utilized with TDCs. For instance, the performance parameters of TDCs such as nonlinearity can

be modeled and optimized via neural networks and machine learning algorithms in FPGAs [66]. Moreover, Internet of things applications and fast AI programs which are also known as edge inference systems take advantage of TDCs to regulate their time-dependent network plans [67].

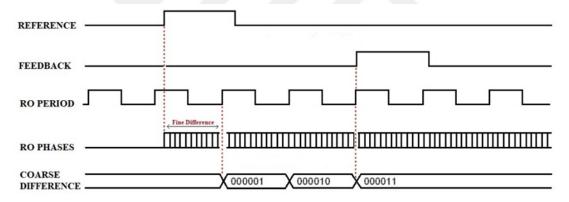

# 2.2.3. Working principle of classical TDCs

Independent from the architecture, the main purpose of the TDCs is to calculate the time difference between incoming signals. In other words, a phase difference between two incoming signals should be converted to digital bits in TDCs. This transformation process relies on ADC functions with small differences. **Figure 2.14** illustrates the well-known working principle of TDCs. The Start signal initiates the counting process and when the stop signals arrive, coarse counting is terminated. Phases of the incoming signals should be recorded first. Then the difference between those recorded points should be measured with a known delay. This known or "reference" interval can be generated via simple delay lines or ring oscillators.

Figure 2.14: Working principle of TDCs.

However, to achieve higher resolutions in state-of-the-art, high-end applications, fine counting can be necessary.

There are common expected parameters from TDCs like high resolution, wide dynamic range, lower power consumption, and low phase noise. On the other hand, these parameters, or trade-offs between them vary among applications.

The output of TDCs is generally calculated as thermometer codes, but there are other ways to obtain the digitized difference. There are various topologies for TDCs that can be used for different implementations in analog and digital domains. Internal structures of these TDCs generally remain the same, which contains delay lines, registers, and

counters. However, the number and type of each element depending on the requirements of the applications.

# 2.2.4. Time-to-Digital Converters architectures

There are numerous types of TDC architectures that were designed to achieve the required performance and make the trade-off between resolution, area, dead time, and detectable range, in literature. Moreover, power consumption, cost, and conversion speed are the other parameters that should be considered during development. The main types of different TDC architectures are demonstrated below.

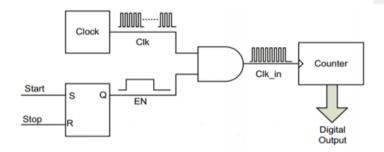

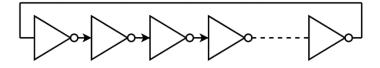

# 2.2.4.1. Counter-based TDC

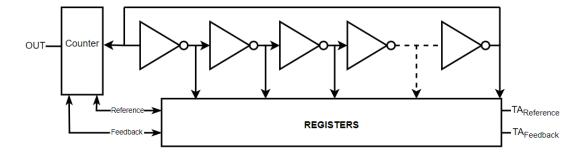

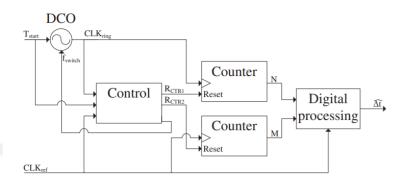

Counter-based architectures can be considered as a primal version of TDCs, which were generally used before the development of sub-micron CMOS devices. For low-resolution applications, in which a couple of nanoseconds is required for conversion, counter-based TDCs can be employed. The main working principle of the counter-based TDCs depends on a high-speed counter architecture. In each clock cycle result of the output is incremented by 1. There are 2 main blocks for the counter-based TDC architecture given in **Figure 2.15**, which are the clock generator and the counter.

Figure 2.15: Counter-based TDC architecture [68].

Start and Stop signals generate an enable signal via SR latch, and this enable signal is used with an inner clock generator to obtain a counter clock [68]. In this method, the difference between the two input clocks can be represented with the inner clock frequency. For instance, if the frequency generator has a 1 GHz clock, and there is a 2 ns difference between clocks, the counter should give "2" as an output. In terms of resolution, phase error signals will always be the integer multiple of the frequency generator's period. For high resolutions, the frequency of the clock generator should be increased but the design of faster counters can be challenging. Also, the power consumption of the clock generator will increase when the output frequency increases. Furthermore, the quality of the generated output highly depends on the phase noise, jitter, and stability of the clock generator [49]. On the other hand, clocks with good spectral purity can be generated via crystal but they increase the cost of the systems as well.

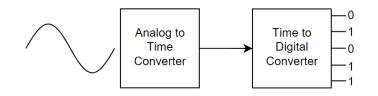

### 2.2.4.2. Analog-to-digital conversion-based TDC

To avoid the disadvantages of using counters to measure the time difference between clocks, Analog-to-Digital converter-based TDCs can be employed in sub-micron CMOS technologies. These architectures take advantage of the advanced developments in ADC design. Combination of TDCs with SAR, sigma-delta modulation, or pipelined ADC architectures give higher resolutions than the other TDCs even with smaller delay times [69].

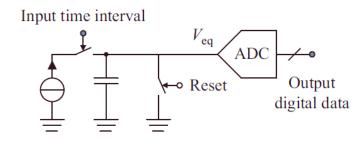

ADC-based TDCs work with a principle of multistep conversion. Instead of directly digitizing the phases, the time difference is converted to voltage first, and then the voltage is quantized to digital bits.

ADC-TDC pairs, which are also known as time-to-voltage converter-based TDCs, consists of two main blocks; an ADC and an integrator. In **Figure 2.16**, blocks of the voltage conversion-based TDC are illustrated.

As it was mentioned before, conversion of the time to voltage can be realized with an integrator. Integration of a voltage between specific time instances can be achieved via a capacitor and constant current source pair. Basically, in a time window that is equal to the difference between 2 input clocks, a capacitor is charged with a current source.

Figure 2.16: Working principle of time-based Analog-to-Digital converter.

After the voltage conversion, the digitization process starts with the ADC. If the working principle in the figure is implemented with Successive-Approximation (SAR) ADCs, resolutions in femtosecond levels can be achieved [69]. The performance of the ADC-based TDCs depends on the type and speed of the ADC and the linearity of the voltage-to-time conversion circuit.

The integrator used in the TDC is generally based on charging capacitors with a current source. These capacitors work in the same manner as charge pumps in analog PLL systems. However, there are also flip-flop-based designs that can be used with extra interpolators [70]. Because of the limited output resistance of the constant current source, linearity degradation may occur during the conversion. Implementing operational amplifier-based integrators was proposed for the solution of the nonlinearity problem [71]. On the other hand, employing op-amps as a voltage-to-time regulator can reduce the digitization speed because of the narrow bandwidth [49]. In **Figure 2.17**, a basic way of voltage-time and time-digital conversion can be seen.

Figure 2.17: ADC based TDC topology [49].

# 2.2.4.3. Delay-line based TDCs

Instead of counting the phase difference between inputs directly, a delayed version of the reference clocks can be generated to obtain finer resolutions. There are various types of architectures that employ delay lines to obtain propagation.

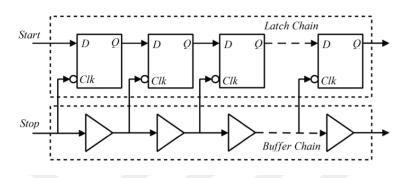

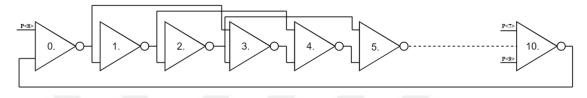

#### Flash (Single Delay Line) TDCs

As it was mentioned before, the most significant parameter of the TDC is its resolution. Previous methods can achieve resolutions that are comparable with the incoming clock period. However, the Flash TDC structure employs uniformly distributed delay lines to achieve lower resolutions.

The phase difference between stages can be changed via design architecture and it only depends on the propagation delay between cells [72]. Mainly, 2 types of delay lines are used in TDCs as a known reference: CMOS inverters and CMOS buffers [73]. When an inverter-based line is used, successive delays have opposite signs and overall oscillation goes with a negative-positive coupling [74]. On the other hand, in buffer-based delay lines, the sign of the delay will be always positive or negative. A positive sign means that phase is logic "1" and the negative sign represents a logic "0". CMOS-based buffers and

inverters are generally limited to a couple of pico-second phase differences between stages. However different topologies such as multi-input and gated delay lines can be used to decrease the delay between stages [75]. The detectable range of the flash TDCs is the multiplication of the number of cells in the delay line and the delay between phases. Flash TDCs have advantages in terms of low latency and simplicity. As it can be seen from **Figure 2.18**, it can be constructed by utilizing two types of elements.

Figure 2.18: Buffer-based Flash TDC [76].

On the other hand, for wider ranges which can be thought of as more bits in the output, the number of the cells in the delay line increases dramatically. Moreover, every single delay between each element should be the same to ensure a linear transfer curve between the phase difference and the error signal. Due to a mismatch between delay-line cells, propagation delay can vary between each element, and it starts to accumulate after each step. At the end of the delay line, accumulation block overflows and the expected output signal cannot be achieved. There are small but significant differences between single delay lines and ring oscillators, and they will be explained in the ring oscillator-based TDCs part.

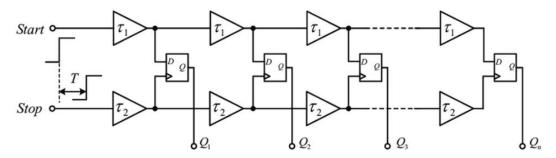

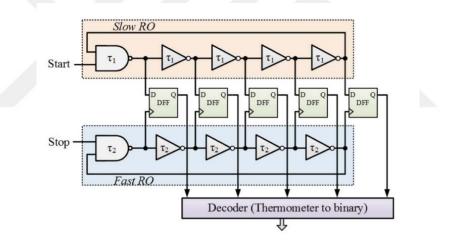

#### Vernier Delay Line TDCs

Instead of using a single delay line to obtain an internal reference for measurement between the time difference of the two input signals, the Vernier delay line method utilizes two different delay lines. To achieve finer resolutions, which can be considered as below 10 picoseconds, and to lower the phase noise of the TDC, the difference between propagation delays of two lines is employed. In other words, the Vernier topology was developed to reduce the resolution of the TDC that cannot be decreased via conventional delay line methods in a given technology.

As shown in **Figure 2.19**, two different delay lines, which have a small difference between their propagation delays, should be constructed as an initial step. The common

applications of the TDCs always include two inputs where one of them is coming before the other one. However, Vernier delay lines utilize this phenomenon to calculate the time difference.

Figure 2.19: Vernier TDC architecture [77].

The first signal is fed to the slower line, which has a bigger propagation delay than the other one, and the second signal is applied to the faster line. After a while registers between delay lines detect the alignment between the delay of the two lines and thermometer-based codes represent the distance between them [78].

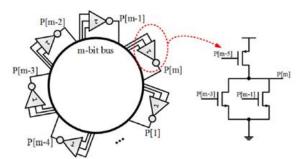

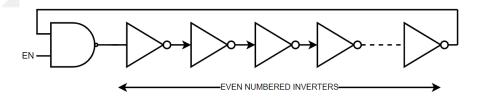

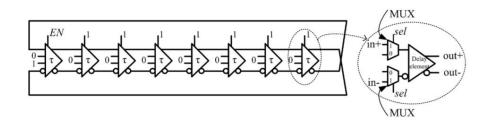

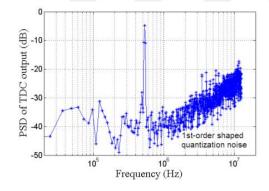

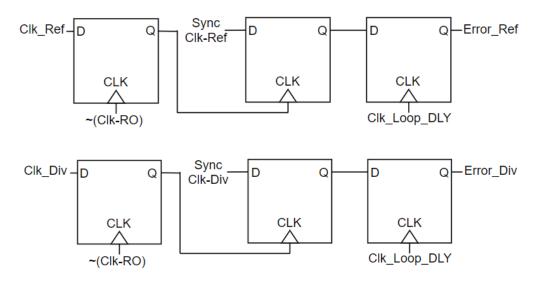

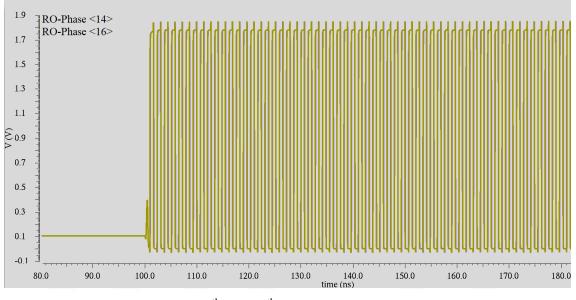

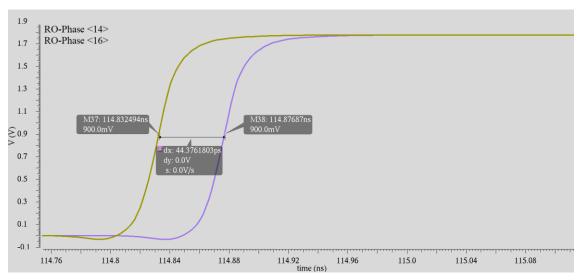

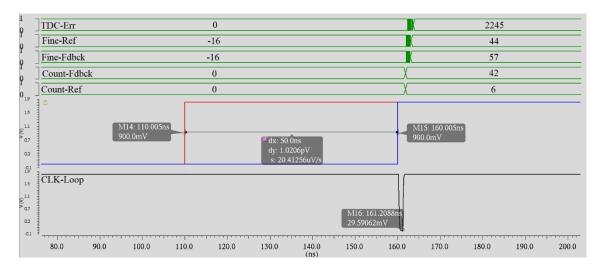

Principally, the resolution only depends on the delay difference between the two lines, but the number of stages and mismatch between the propagation delay of each element are also effective on the overall detection resolution.